2022年超大規(guī)模集成電路可測性設(shè)計(jì)(DFT)技術(shù)與實(shí)踐培訓(xùn)綜述

隨著集成電路工藝節(jié)點(diǎn)持續(xù)微縮,芯片規(guī)模與復(fù)雜度呈指數(shù)級增長,可測性設(shè)計(jì)已成為確保芯片功能正確、提升良率、控制成本的關(guān)鍵環(huán)節(jié)。2022年,針對超大規(guī)模集成電路的可測性設(shè)計(jì)技術(shù)與實(shí)踐培訓(xùn),緊密圍繞產(chǎn)業(yè)前沿需求,系統(tǒng)性地探討了DFT的核心原理、關(guān)鍵技術(shù)及工程實(shí)現(xiàn)。

一、培訓(xùn)核心內(nèi)容聚焦

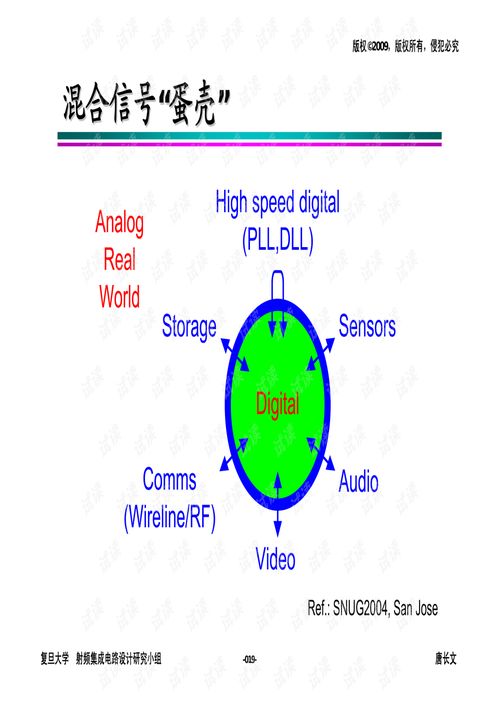

本次培訓(xùn)深入剖析了超大規(guī)模集成電路面臨的測試挑戰(zhàn),如測試數(shù)據(jù)量爆炸、測試功耗控制、測試時間壓縮等。核心教學(xué)內(nèi)容覆蓋了三大DFT主流技術(shù):

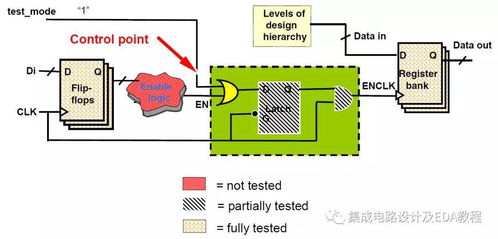

1. 掃描設(shè)計(jì):詳細(xì)講解了全掃描與部分掃描設(shè)計(jì)方法,包括掃描鏈插入、時鐘控制、測試向量生成與壓縮技術(shù),重點(diǎn)探討了如何平衡面積開銷與測試覆蓋率。

2. 內(nèi)建自測試:系統(tǒng)介紹了存儲器BIST和邏輯BIST的架構(gòu)設(shè)計(jì)、算法實(shí)現(xiàn)及結(jié)果分析,強(qiáng)調(diào)了在SoC中嵌入BIST模塊以實(shí)現(xiàn)高效自檢的策略。

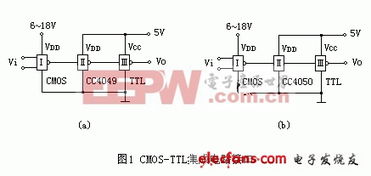

3. 邊界掃描:依據(jù)IEEE 1149.1等標(biāo)準(zhǔn),闡述了邊界掃描在板級與芯片級互聯(lián)測試、內(nèi)核測試中的應(yīng)用,并探討了其在系統(tǒng)級調(diào)試中的作用。

培訓(xùn)還涉及了基于ATPG的故障模型、測試功耗管理、可測試性設(shè)計(jì)規(guī)則檢查等高級議題。

二、實(shí)踐與工具環(huán)節(jié)

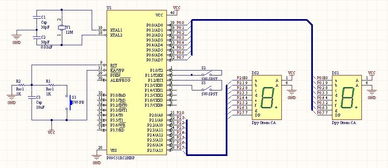

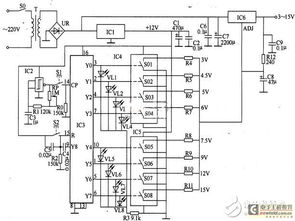

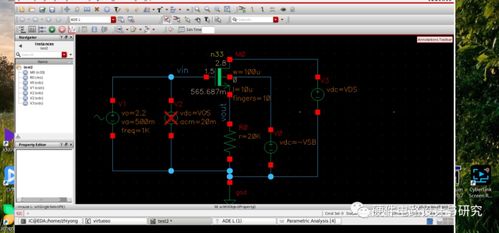

理論與實(shí)踐相結(jié)合是本次培訓(xùn)的亮點(diǎn)。通過主流EDA工具(如Synopsys、Cadence、Siemens EDA的相關(guān)DFT工具鏈)的上機(jī)操作,學(xué)員親身體驗(yàn)了從RTL設(shè)計(jì)插入DFT結(jié)構(gòu),到生成測試向量并進(jìn)行故障仿真的完整流程。實(shí)踐案例聚焦于當(dāng)前熱門的先進(jìn)工藝節(jié)點(diǎn)芯片和復(fù)雜SoC,使學(xué)員能夠直面高速接口測試、低功耗設(shè)計(jì)測試等實(shí)際工程難題。

三、行業(yè)趨勢與展望

培訓(xùn)結(jié)合2022年技術(shù)動態(tài),展望了DFT的未來發(fā)展方向:

- 與AI/ML融合:利用機(jī)器學(xué)習(xí)優(yōu)化測試向量生成、故障診斷和良率分析。

- 面向3D-IC與Chiplet:探討了堆疊芯片和異構(gòu)集成中新的可測試性挑戰(zhàn)與解決方案,如跨die測試訪問。

- 全生命周期測試:強(qiáng)調(diào)DFT技術(shù)需支持芯片從生產(chǎn)測試到系統(tǒng)現(xiàn)場運(yùn)行的健康監(jiān)控與預(yù)測性維護(hù)。

2022年的DFT技術(shù)與實(shí)踐培訓(xùn),不僅夯實(shí)了學(xué)員在可測性設(shè)計(jì)領(lǐng)域的基礎(chǔ)理論,更通過前沿案例與工具實(shí)踐,提升了解決超大規(guī)模集成電路測試工程問題的綜合能力,為助力我國集成電路產(chǎn)業(yè)攻克高端芯片測試壁壘提供了重要的人才與技術(shù)支撐。

如若轉(zhuǎn)載,請注明出處:http://m.plenties.com.cn/product/67.html

更新時間:2026-03-01 11:26:45